As the semiconductor industry hits the physical limits of traditional silicon and organic packaging, a new material is emerging as the savior of Moore’s Law: glass. As we approach the FLEX Technology Summit 2026 in Arizona this February, the industry is buzzing with the realization that the future of frontier AI models—and the "super-chips" required to run them—no longer hinges solely on smaller transistors, but on the glass foundations they sit upon.

The shift toward glass substrates represents a fundamental pivot in chip architecture. For decades, the industry relied on organic (plastic-based) materials to connect chips to circuit boards. However, the massive power demands and extreme heat generated by next-generation AI processors have pushed these materials to their breaking point. The upcoming summit in Arizona is expected to showcase how glass, with its superior flatness and thermal stability, is enabling the creation of multi-die "super-chips" that were previously thought to be physically impossible to manufacture.

The End of the "Warpage Wall" and the Rise of Glass Core

The technical primary driver behind this shift is the "warpage wall." Traditional organic substrates, such as those made from Ajinomoto Build-up Film (ABF), are prone to bending and shrinking when subjected to the intense heat of modern AI workloads. This warpage causes tiny connections between the chip and the substrate to crack or disconnect. Glass, by contrast, possesses a Coefficient of Thermal Expansion (CTE) that closely matches silicon, ensuring that the entire package expands and contracts at the same rate. This allows for the creation of massive "monster" packages—some exceeding 100mm x 100mm—that can house dozens of high-bandwidth memory (HBM) stacks and compute dies in a single, unified module.

Beyond structural integrity, glass substrates offer a 10x increase in interconnect density. While organic materials struggle to maintain signal integrity at wiring widths below 5 micrometers, glass can support sub-2-micrometer lines. This precision is critical for the upcoming NVIDIA (NASDAQ:NVDA) "Rubin" architecture, which is rumored to require over 50,000 I/O connections to manage the 19.6 TB/s bandwidth of HBM4 memory. Furthermore, glass acts as a superior insulator, reducing dielectric loss by up to 60% and significantly cutting the power required for data movement within the chip.

Initial reactions from the research community have been overwhelmingly positive, though cautious. Experts at the FLEX Summit are expected to highlight that while glass solves the thermal and density issues, it introduces new challenges in handling and fragility. Unlike organic substrates, which are relatively flexible, glass is brittle and requires entirely new manufacturing equipment. However, with Intel (NASDAQ:INTC) already announcing high-volume manufacturing (HVM) at its Chandler, Arizona facility, the industry consensus is that the benefits far outweigh the logistical hurdles.

The Global "Glass Arms Race"

This technological shift has sparked a high-stakes race among the world's largest chipmakers. Intel (NASDAQ:INTC) has taken an early lead, recently shipping its Xeon 6+ "Clearwater Forest" processors, the first commercial products to feature a glass core substrate. By positioning its glass manufacturing hub in Arizona—the very location of the upcoming FLEX Summit—Intel is aiming to regain its crown as the leader in advanced packaging, a sector currently dominated by TSMC (NYSE:TSM).

Not to be outdone, Samsung Electronics (KRX:005930) has accelerated its "Dream Substrate" program, leveraging its expertise in glass from its display division to target mass production by the second half of 2026. Meanwhile, SKC (KRX:011790), through its subsidiary Absolics, has opened a state-of-the-art facility in Georgia, supported by $75 million in US CHIPS Act funding. This facility is reportedly already providing samples to AMD (NASDAQ:AMD) for its next-generation Instinct accelerators. The strategic advantage for these companies is clear: those who master glass packaging first will become the primary suppliers for the "super-chips" that power the next decade of AI innovation.

For tech giants like Microsoft (NASDAQ:MSFT) and Alphabet (NASDAQ:GOOGL), who are designing their own custom AI silicon (ASICs), the availability of glass substrates means they can pack more performance into each rack of their data centers. This could disrupt the existing market by allowing smaller, more efficient AI clusters to outperform current massive liquid-cooled installations, potentially lowering the barrier to entry for training frontier-scale models.

Sustaining Moore’s Law in the AI Era

The emergence of glass substrates is more than just a material upgrade; it is a critical milestone in the broader AI landscape. As AI scaling laws demand exponentially more compute, the industry has transitioned from a "monolithic" approach (one big chip) to "heterogeneous integration" (many small chips, or chiplets, working together). Glass is the "interposer" that makes this integration possible at scale. Without it, the roadmap for AI hardware would likely stall as organic materials fail to support the sheer size of the next generation of processors.

This development also carries significant geopolitical implications. The heavy investment in Arizona and Georgia by Intel and SKC respectively highlights a concerted effort to "re-shore" advanced packaging capabilities to the United States. Historically, while chip design occurred in the US, the "back-end" packaging was almost entirely outsourced to Asia. The shift to glass represents a chance for the US to secure a vital part of the AI supply chain, mitigating risks associated with regional dependencies.

However, concerns remain regarding the environmental impact and yield rates of glass. The high temperatures required for glass processing and the potential for breakage during high-speed assembly could lead to initial supply constraints. Comparison to previous milestones, such as the move from aluminum to copper interconnects in the late 1990s, suggests that while the transition will be difficult, it is a necessary evolution for the industry to move forward.

Future Horizons: From Glass to Light

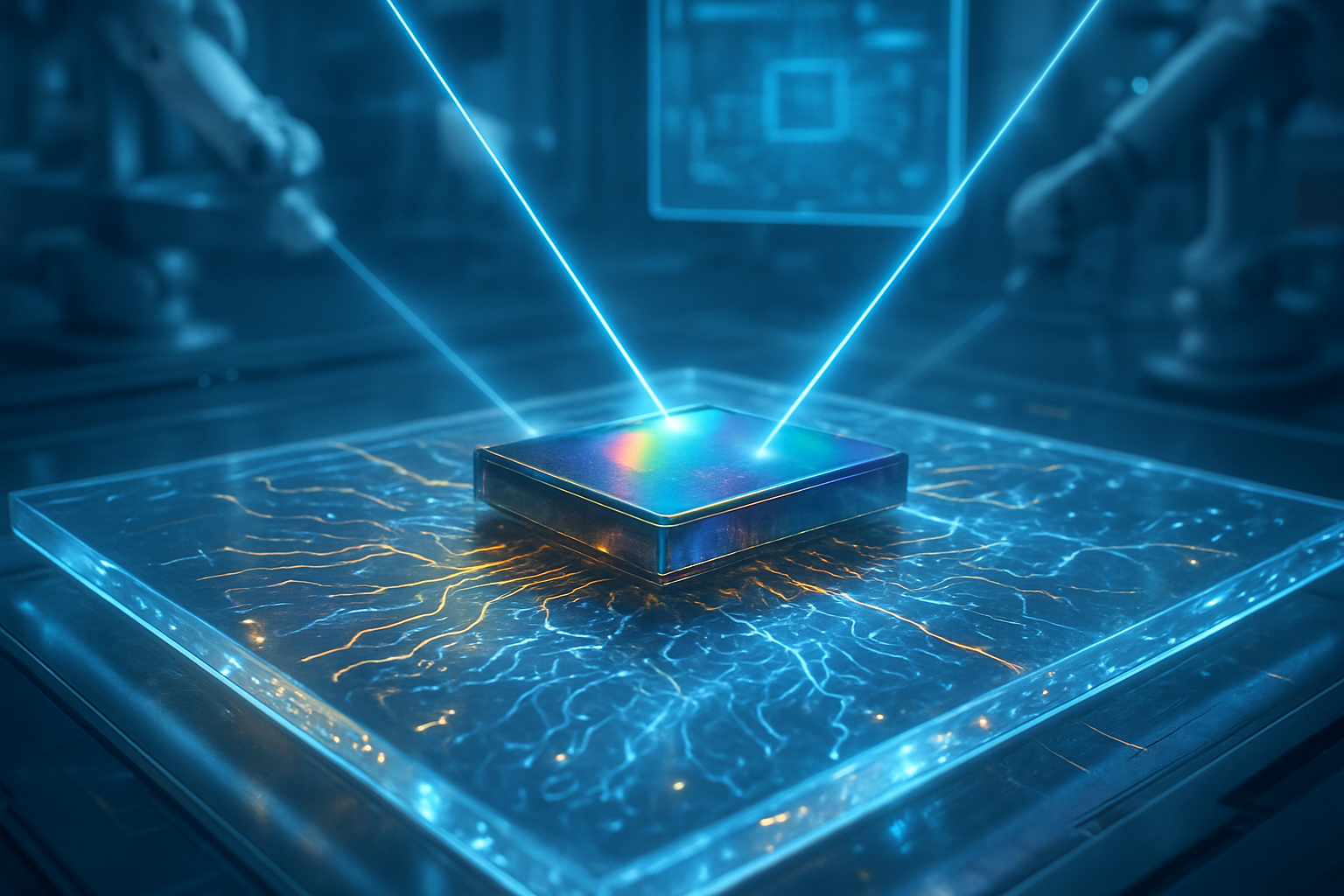

Looking ahead, the FLEX Technology Summit 2026 is expected to provide a glimpse into the "Feynman" era of chip design, named after the physicist Richard Feynman. Experts predict that glass substrates will eventually serve as the medium for Co-Packaged Optics (CPO). Because glass is transparent, it can house optical waveguides directly within the substrate, allowing chips to communicate using light (photons) rather than electricity (electrons). This would virtually eliminate heat from data movement and could boost AI inference performance by another 5x to 10x by the end of the decade.

In the near term, we expect to see "hybrid" substrates that combine organic layers with a glass core, providing a balance between durability and performance. Challenges such as developing "through-glass vias" (TGVs) that can reliably carry high currents without cracking the glass remain a primary focus for engineers. If these challenges are addressed, the mid-2020s will be remembered as the era when the "glass ceiling" of semiconductor physics was finally shattered.

A New Foundation for Intelligence

The transition to glass substrates and advanced 3D packaging marks a definitive shift in the history of artificial intelligence. It signifies that we have moved past the era where software and algorithms were the primary bottlenecks; today, the bottleneck is the physical substrate upon which intelligence is built. The developments being discussed at the FLEX Technology Summit 2026 represent the hardware foundation that will support the next generation of AGI-seeking models.

As we look toward the coming weeks and months, the industry will be watching for yield data from Intel’s Arizona fabs and the first performance benchmarks of NVIDIA’s glass-enabled Rubin GPUs. The "Glass Age" is no longer a theoretical projection; it is a manufacturing reality that will define the winners and losers of the AI revolution.

This content is intended for informational purposes only and represents analysis of current AI developments.

TokenRing AI delivers enterprise-grade solutions for multi-agent AI workflow orchestration, AI-powered development tools, and seamless remote collaboration platforms. For more information, visit https://www.tokenring.ai/.