In a definitive signal that the artificial intelligence revolution is only accelerating, Taiwan Semiconductor Manufacturing Company (NYSE: TSM) reported staggering record-breaking financial results for the fourth quarter of 2025. On January 15, 2026, the world’s largest contract chipmaker revealed that its quarterly net income surged 35% year-over-year to NT$505.74 billion (approximately US$16.01 billion), far exceeding analyst expectations and cementing its role as the indispensable foundation of the global AI economy.

The results highlight a historic shift in the semiconductor landscape: for the first time, High-Performance Computing (HPC) and AI applications accounted for 58% of the company's annual revenue, officially dethroning the smartphone segment as TSMC’s primary growth engine. This "AI megatrend," as described by TSMC leadership, has pushed the company to a record quarterly revenue of US$33.73 billion, as tech giants scramble to secure the advanced silicon necessary to power the next generation of large language models and autonomous systems.

The Push for 2nm and Beyond

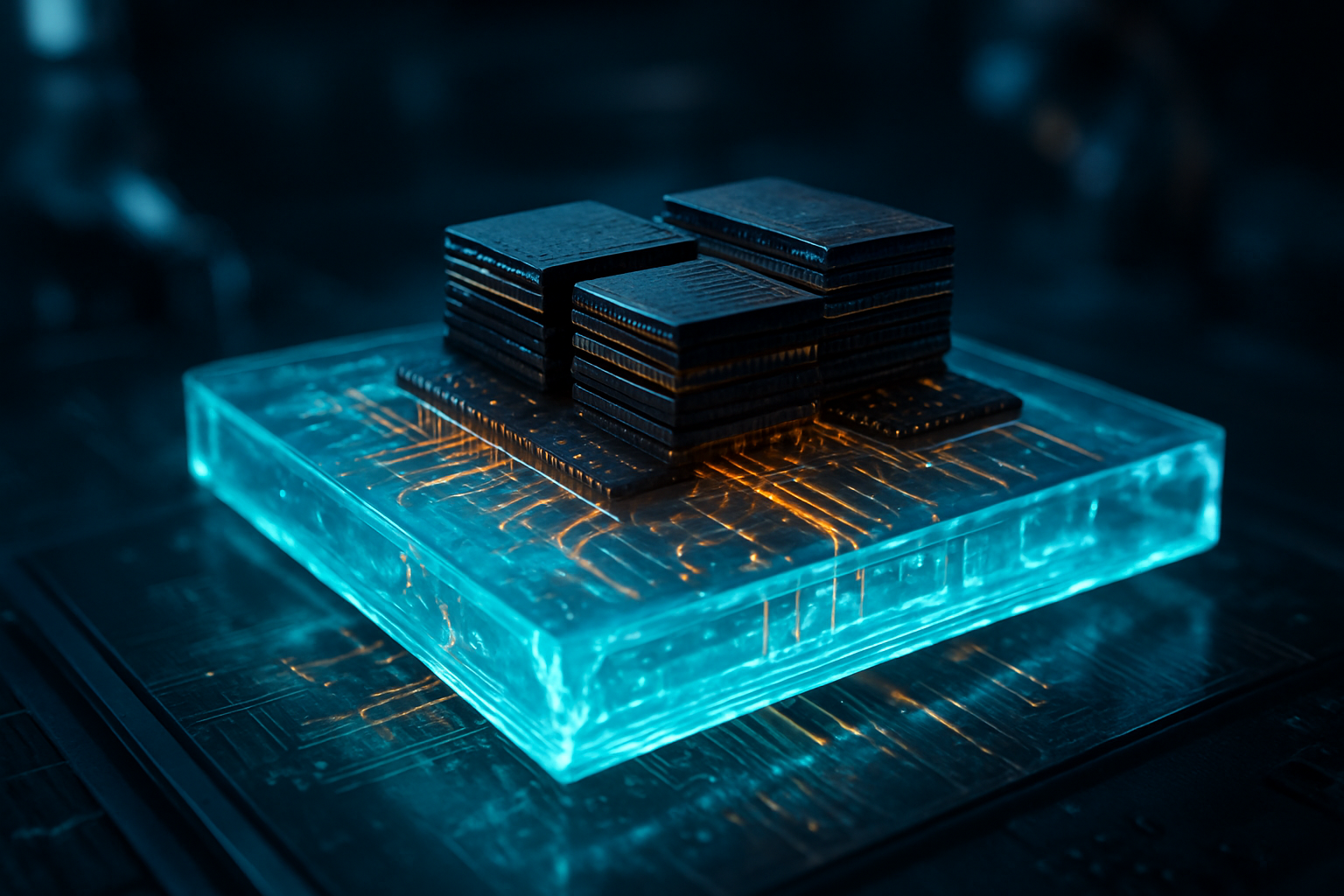

The technical milestones achieved in Q4 2025 represent a significant leap forward in Moore’s Law. TSMC officially announced the commencement of high-volume manufacturing (HVM) for its 2-nanometer (N2) process node at its Hsinchu and Kaohsiung facilities. The N2 node marks a radical departure from previous generations, utilizing the company’s first-generation nanosheet (Gate-All-Around or GAA) transistor architecture. This transition away from the traditional FinFET structure allows for a 10–15% increase in speed or a 25–30% reduction in power consumption compared to the already industry-leading 3nm (N3E) process.

Furthermore, advanced technologies—classified as 7nm and below—now account for a massive 77% of TSMC’s total wafer revenue. The 3nm node has reached full maturity, contributing 28% of the quarter’s revenue as it powers the latest flagship mobile devices and AI accelerators. Industry experts have lauded TSMC’s ability to maintain a 62.3% gross margin despite the immense complexity of ramping up GAA architecture, a feat that competitors have struggled to match. Initial reactions from the research community suggest that the successful 2nm ramp-up effectively grants the AI industry a two-year head start on realizing complex "agentic" AI systems that require extreme on-chip efficiency.

Market Implications for Tech Giants

The implications for the "Magnificent Seven" and the broader startup ecosystem are profound. NVIDIA (NASDAQ: NVDA), the primary architect of the AI boom, remains TSMC’s largest customer for high-end AI GPUs, but the Q4 results show a diversifying base. Apple (NASDAQ: AAPL) has secured the lion’s share of initial 2nm capacity for its upcoming silicon, while Advanced Micro Devices (NASDAQ: AMD) and various hyperscalers developing custom ASICs—including Google's parent Alphabet (NASDAQ: GOOGL) and Amazon (NASDAQ: AMZN)—are aggressively vying for space on TSMC's production lines.

TSMC’s strategic advantage is further bolstered by its massive expansion of CoWoS (Chip on Wafer on Substrate) advanced packaging capacity. By resolving the "packaging crunch" that bottlenecked AI chip supply throughout 2024 and early 2025, TSMC has effectively shortened the lead times for enterprise-grade AI hardware. This development places immense pressure on rival foundries like Intel (NASDAQ: INTC) and Samsung, who must now race to prove their own GAA implementations can achieve comparable yields. For startups, the increased supply of AI silicon means more affordable compute credits and a faster path to training specialized vertical models.

The Global AI Landscape and Strategic Concerns

Looking at the broader landscape, TSMC’s performance serves as a powerful rebuttal to skeptics who predicted an "AI bubble" burst in late 2025. Instead, the data suggests a permanent structural shift in global computing. The demand is no longer just for "training" chips but is increasingly shifting toward "inference" at scale, necessitating the high-efficiency 2nm and 3nm chips TSMC is uniquely positioned to provide. This milestone marks the first time in history that a single foundry has held such a critical bottleneck over the most transformative technology of a generation.

However, this dominance brings significant geopolitical and environmental scrutiny. To mitigate concentration risks, TSMC confirmed it is accelerating its Arizona footprint, applying for permits for a fourth factory and its first U.S.-based advanced packaging plant. This move aims to create a "manufacturing cluster" in North America, addressing concerns about supply chain resilience in the Taiwan Strait. Simultaneously, the energy requirements of these advanced fabs remain a point of contention, as the power-hungry EUV (Extreme Ultraviolet) lithography machines required for 2nm production continue to challenge global sustainability goals.

Future Roadmaps and 1.6nm Ambitions

The roadmap for 2026 and beyond looks even more aggressive. TSMC announced a record-shattering capital expenditure budget of US$52 billion to US$56 billion for the coming year, with up to 80% dedicated to advanced process technologies. This investment is geared toward the upcoming N2P node, an enhanced version of the 2nm process, and the even more ambitious A16 (1.6-nanometer) node, which is slated for volume production in the second half of 2026. The A16 process will introduce backside power delivery, a technical revolution that separates the power circuitry from the signal circuitry to further maximize performance.

Experts predict that the focus will soon shift from pure transistor density to "system-level" scaling. This includes the integration of high-bandwidth memory (HBM4) and sophisticated liquid cooling solutions directly into the chip packaging. The challenge remains the physical limits of silicon; as transistors approach the atomic scale, the industry must solve unprecedented thermal and quantum tunneling issues. Nevertheless, TSMC’s guidance of nearly 30% revenue growth for 2026 suggests they are confident in their ability to overcome these hurdles.

Summary of the Silicon Era

In summary, TSMC’s Q4 2025 earnings report is more than just a financial statement; it is a confirmation that the AI era is still in its high-growth phase. By successfully transitioning to 2nm GAA technology and significantly expanding its advanced packaging capabilities, TSMC has cleared the path for more powerful, efficient, and accessible artificial intelligence. The company’s record-breaking $16 billion quarterly profit is a testament to its status as the gatekeeper of modern innovation.

In the coming weeks and months, the market will closely monitor the yields of the new 2nm lines and the progress of the Arizona expansion. As the first 2nm-powered consumer and enterprise products hit the market later this year, the gap between those with access to TSMC’s "leading-edge" silicon and those without will likely widen. For now, the global tech industry remains tethered to a single island, waiting for the next batch of silicon that will define the future of intelligence.

This content is intended for informational purposes only and represents analysis of current AI developments.

TokenRing AI delivers enterprise-grade solutions for multi-agent AI workflow orchestration, AI-powered development tools, and seamless remote collaboration platforms.

For more information, visit https://www.tokenring.ai/.