The semiconductor industry has reached a historic inflection point. For five decades, the industry followed the traditional Moore’s Law, doubling transistor density by physically shrinking the components on a single piece of silicon. However, as of February 2026, that "geometrical scaling" has hit a physical and economic wall. In its place, a "New Moore’s Law"—more accurately described as System-level Moore’s Law—has emerged, shifting the focus from the individual chip to the entire package. This evolution is driven by the insatiable compute demands of generative AI, where performance is no longer defined by how many transistors can fit on a die, but by how many dies can be seamlessly stitched together in 3D space.

The primary engines of this revolution are Chip-on-Wafer-on-Substrate (CoWoS) and vertical 3D stacking technologies. By abandoning the "monolithic" approach—where a processor is carved from a single piece of silicon—industry leaders are now building massive, multi-die systems that bypass the traditional limits of physics. This shift represents the most significant architectural change in computing history since the invention of the integrated circuit, effectively decoupling performance gains from the slow and increasingly expensive progress of lithography nodes.

The Death of the Monolithic Die and the Rise of CoWoS-L

The technical heart of this shift lies in overcoming the "reticle limit." For years, the maximum size of a single chip was restricted to approximately 858mm²—the physical size of the mask used in lithography. To build the massive processors required for 2026-era AI, such as the NVIDIA (NASDAQ: NVDA) Rubin R100, engineers have turned to Advanced Packaging. TSMC (NYSE: TSM) has pioneered CoWoS-L (Local Silicon Interconnect), which uses tiny silicon bridges to "stitch" multiple logic dies together on an organic substrate. This allows a single package to effectively behave as one massive processor, far exceeding the physical size limits of traditional manufacturing.

Beyond mere size, the industry has moved into the realm of true 3D integration with System on Integrated Chips (SoIC). Unlike 2.5D packaging, where chips sit side-by-side, SoIC allows for "bumpless" hybrid bonding, stacking logic directly on top of logic or memory. This reduces the distance data must travel from millimeters to micrometers, slashing power consumption and nearly eliminating the latency that previously throttled AI performance. Initial reactions from the research community have been transformative; experts note that the interconnect density provided by SoIC is now a more critical metric for AI training speeds than the raw clock speed of the transistors themselves.

Strategic Realignment: The System Foundry Model

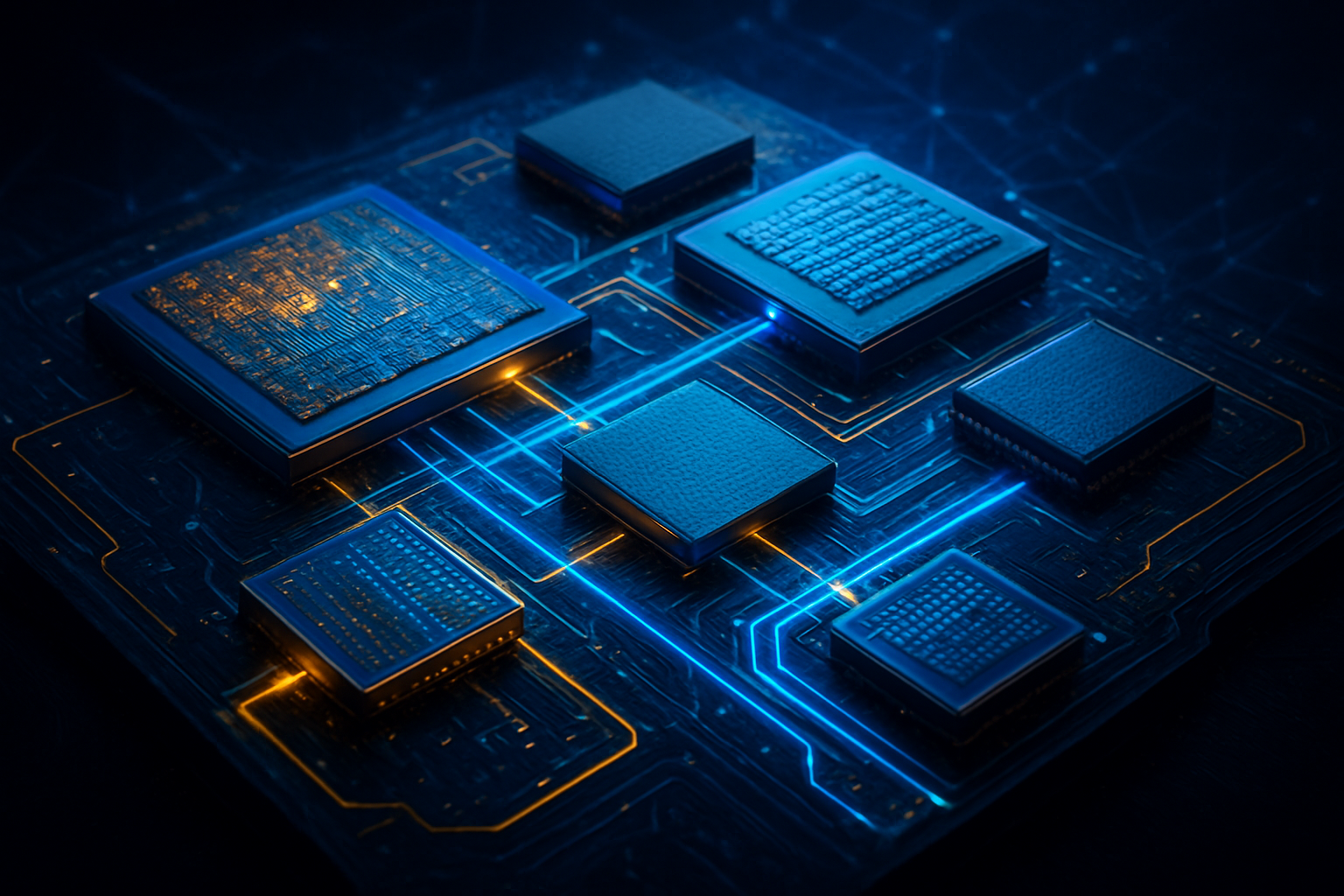

This transition has fundamentally altered the competitive landscape for tech giants and foundries. TSMC has maintained its dominance by aggressively expanding its advanced packaging capacity to over 140,000 wafers per month in early 2026. This "System Foundry" approach allows them to offer a full-stack solution: 2nm logic, 3D stacking, and CoWoS-L packaging. Meanwhile, Intel (NASDAQ: INTC) has pivoted its strategy to position its Advanced System Assembly and Test (ASAT) business as a standalone service. By offering Foveros Direct 3D and EMIB packaging to external customers, Intel is attempting to capture the growing market for custom AI ASICs from cloud providers like Amazon and Google.

Advanced Micro Devices (NASDAQ: AMD) has also leveraged these developments to close the gap with market leaders. The newly released Instinct MI400 series utilizes SoIC-X technology to stack HBM4 memory directly onto the GPU logic, achieving a staggering 20 TB/s of memory bandwidth. This strategic move highlights the "Memory Wall" as the primary bottleneck in LLM training; by using vertical integration, AMD can provide memory capacities that were physically impossible under old monolithic designs. For startups and smaller AI labs, the emergence of chiplet "standardization" means they can now design custom accelerators using off-the-shelf high-performance chiplets, lowering the barrier to entry for specialized AI hardware.

Solving the "Warpage Wall" and the Memory Bottleneck

The wider significance of the "New Moore's Law" extends beyond performance; it is a response to the "Warpage Wall." As packages grow larger than 100mm per side to accommodate dozens of chiplets, traditional organic substrates tend to warp under the intense heat generated by 1,000-watt AI GPUs. This has led to the first commercial rollout of glass substrates in early 2026, led by Intel and Samsung (KOSPI: 005930). Glass provides superior thermal stability and flatness, enabling the ultra-fine interconnects required for next-generation 3D stacking.

Furthermore, this era marks the beginning of the "System Technology Co-Optimization" (STCO) phase. Previously, chip design and packaging were separate steps; now, they are unified. This fits into the broader AI landscape by addressing the catastrophic power consumption of modern data centers. By integrating Silicon Photonics and Co-Packaged Optics (CPO) directly into the package, companies can now convert electrical signals to light within the processor itself. This bypasses the energy-intensive process of pushing electrons through copper cables, a milestone that compares in significance to the transition from vacuum tubes to transistors.

The Road to the Trillion-Transistor Package

Looking ahead, the industry is aligned on a singular goal: the trillion-transistor package by 2030. In the near term, we expect to see the "Base Die" revolution, where the bottom layer of a 3D stack handles all power delivery and routing, leaving the top layers dedicated purely to computation. This will likely lead to "liquid-to-chip" cooling becoming a standard requirement for high-end AI clusters, as the heat density of 3D-stacked chips begins to exceed the limits of traditional air and even current water-cooling methods.

However, challenges remain. The complexity of testing 3D-stacked chips is immense—if one "chiplet" in a stack of ten is faulty, the entire expensive package may be lost. Experts predict that "Self-Healing Silicon," which can reroute circuits around manufacturing defects in real-time, will be the next major area of research. Additionally, the geopolitical concentration of advanced packaging capacity in Taiwan remains a point of concern for global supply chain resilience, prompting a frantic race to build similar facilities in the United States and Europe.

A New Architecture for a New Era

The evolution of chiplets and CoWoS represents more than just a clever engineering workaround; it is a fundamental shift in how humanity builds thinking machines. The "New Moore’s Law" acknowledges that while we can no longer make transistors significantly smaller, we can make the systems they inhabit significantly more complex and efficient. The transition from 2D to 3D, and from copper to light, ensures that the AI revolution will not be throttled by the physical limits of a single silicon wafer.

As we move through 2026, the primary metric of progress will be "transistors per package." With the arrival of glass substrates, HBM4, and 3D SoIC, the roadmap for AI hardware has been extended by another decade. The coming months will be defined by the "Packaging Wars," as foundries and chip designers race to secure the capacity needed to build the world’s most powerful systems. The monolithic era is over; the era of the integrated system has begun.

This content is intended for informational purposes only and represents analysis of current AI developments.

TokenRing AI delivers enterprise-grade solutions for multi-agent AI workflow orchestration, AI-powered development tools, and seamless remote collaboration platforms.

For more information, visit https://www.tokenring.ai/.