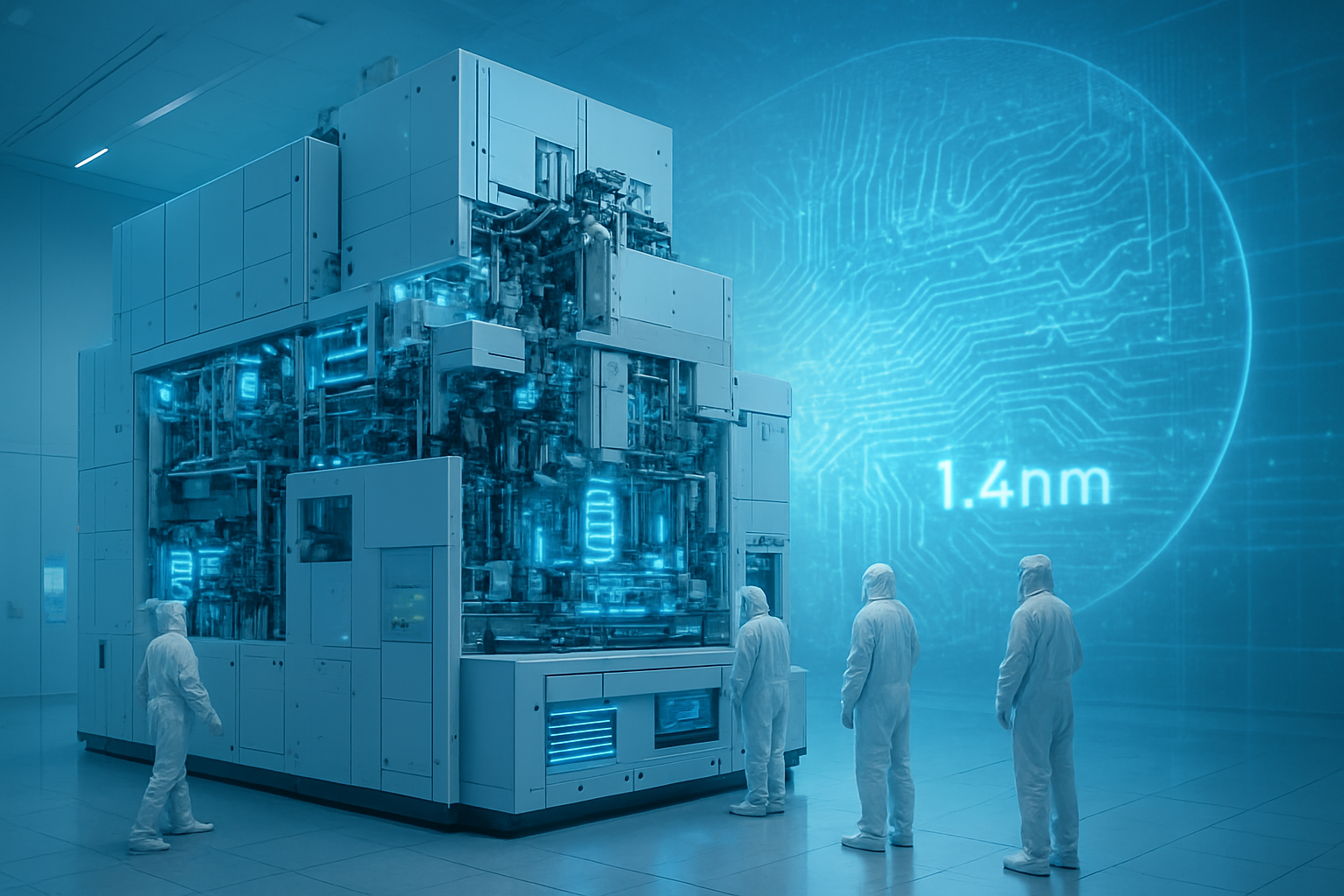

In a move that significantly alters the competitive landscape of global chip manufacturing, Intel Corporation (NASDAQ: INTC) has announced the successful installation and acceptance testing of its second ASML Holding N.V. (NASDAQ: ASML) High-NA EUV lithography system. Located at Intel's premier D1X research and development facility in Hillsboro, Oregon, this second unit—specifically the production-ready Twinscan EXE:5200B—marks the transition from experimental research to the practical implementation of the company's 1.4nm (14A) process node. As of late January 2026, Intel stands alone as the only semiconductor manufacturer in the world to have successfully operationalized a High-NA fleet, effectively stealing a march on long-time rivals in the race to sustain Moore’s Law.

The immediate significance of this development cannot be overstated; it represents the first major technological "leapfrog" in a decade where Intel has definitively outpaced its competitors in adopting next-generation manufacturing tools. While the first EXE:5000 system, delivered in 2024, served as a testbed for engineers to master the complexities of High-NA optics, the new EXE:5200B is a high-volume manufacturing (HVM) workhorse. With a verified throughput of 175 wafers per hour, Intel is now positioned to prove that geometric scaling at the 1.4nm level is not only technically possible but economically viable for the massive AI and high-performance computing (HPC) markets.

Breaking the Resolution Barrier: The Technical Prowess of the EXE:5200B

The transition to High-NA (High Numerical Aperture) EUV is the most significant shift in lithography since the introduction of standard EUV nearly a decade ago. At the heart of the EXE:5200B is a sophisticated anamorphic optical system that increases the numerical aperture from 0.33 to 0.55. This improvement allows for an 8nm resolution, a sharp contrast to the 13nm limit of current systems. By achieving this level of precision, Intel can print the most critical features of its 14A process node in a single exposure. Previously, achieving such density required "multi-patterning," a process where a single layer is split into multiple lithographic steps, which significantly increases the risk of defects, manufacturing time, and cost.

The EXE:5200B specifically addresses the throughput concerns that plagued early EUV adoption. Reaching 175 wafers per hour (WPH) is a critical milestone for HVM readiness; it ensures that the massive capital expenditure of nearly $400 million per machine can be amortized across a high volume of chips. This model features an upgraded EUV light source and a redesigned wafer handling system that minimizes idle time. Initial reactions from the semiconductor research community suggest that Intel’s ability to hit these throughput targets ahead of schedule has validated the company’s "aggressive first-mover" strategy, which many analysts previously viewed as a high-risk gamble.

In addition to resolution improvements, the EXE:5200B offers a refined overlay accuracy of 0.7 nanometers. This is essential for the 1.4nm era, where even an atomic-scale misalignment between chip layers can render a processor useless. By integrating this tool with its second-generation RibbonFET gate-all-around (GAA) transistors and PowerVia backside power delivery, Intel is constructing a manufacturing stack that differs fundamentally from the FinFET architectures that dominated the last decade. This holistic approach to scaling is what Intel believes will allow it to regain the performance-per-watt crown by 2027.

Shifting Tides: Competitive Implications for the Foundry Market

The successful rollout of High-NA EUV has immediate strategic implications for the "Big Three" of semiconductor manufacturing. For Intel, this is a cornerstone of its "five nodes in four years" ambition, providing the technical foundation to attract high-margin clients to its Intel Foundry business. Reports indicate that major AI chip designers, including NVIDIA Corporation (NASDAQ: NVDA) and Apple Inc. (NASDAQ: AAPL), are already evaluating Intel’s 14A Process Development Kit (PDK) version 0.5. With Taiwan Semiconductor Manufacturing Company (NYSE: TSM) reportedly facing capacity constraints for its upcoming 2nm nodes, Intel’s High-NA lead offers a compelling domestic alternative for US-based fabless firms looking to diversify their supply chains.

Conversely, TSMC has maintained a more cautious stance, signaling that it may not adopt High-NA EUV until 2028 or later, likely with its A10 node. The Taiwanese giant is betting that it can extend the life of standard 0.33 NA EUV through advanced multi-patterning and "Low-NA" optimizations to keep costs lower for its customers in the short term. However, Intel’s move forces TSMC to defend its dominance in a way it hasn't had to in years. If Intel can demonstrate superior yields and lower cycle times on its 14A node thanks to the EXE:5200B's single-exposure capabilities, the economic argument for TSMC’s caution could quickly evaporate, potentially leading to a market share shift in the high-end AI accelerator space.

Samsung Electronics (KRX: 005930) also finds itself in a challenging middle ground. While Samsung has begun receiving High-NA components, it remains behind Intel in terms of system integration and validation. This gap provides Intel with a window of opportunity to secure "anchor tenants" for its 14A node. Strategic advantages are also emerging for specialized AI startups that require the absolute highest transistor density for next-generation neural processing units (NPUs). By being the first to offer 1.4nm-class manufacturing, Intel is positioning its Oregon and Ohio sites as the epicenter of global AI hardware development.

The Trillion-Dollar Tool: Geopolitics and the Future of Moore’s Law

The arrival of the EXE:5200B in Portland is more than a corporate milestone; it is a critical event in the broader landscape of technological sovereignty. As AI models grow exponentially in complexity, the demand for compute density has become a matter of national economic security. The ability to manufacture at the 1.4nm level using High-NA EUV is the "frontier" of human engineering. This development effectively extends the lifespan of Moore’s Law for at least another decade, quieting critics who argued that physical limits and economic costs would stall geometric scaling at 3nm.

However, the $380 million to $400 million price tag per machine raises significant concerns about the concentration of manufacturing power. Only a handful of companies can afford the multibillion-dollar capital expenditure required to build a High-NA-capable fab. This creates a high barrier to entry that could further consolidate the industry, leaving smaller foundries unable to compete at the leading edge. Furthermore, the reliance on a single supplier—ASML—for this essential technology remains a potential bottleneck in the global supply chain, a fact that has not gone unnoticed by trade regulators and government bodies overseeing the CHIPS Act.

Comparisons are already being drawn to the initial EUV rollout in 2018-2019, which saw TSMC take a definitive lead over Intel. In 2026, the roles appear to be reversed. The industry is watching to see if Intel can avoid the yield pitfalls that historically hampered its transitions. If successful, the 1.4nm roadmap fueled by High-NA EUV will be remembered as the moment the semiconductor industry successfully navigated the "post-FinFET" transition, enabling the trillion-parameter AI models of the late 2020s.

The Road to Hyper-NA and 10A Nodes

Looking ahead, the installation of the second EXE:5200B is merely the beginning of a long-term scaling roadmap. Intel expects to begin "risk production" on its 14A node by 2027, with high-volume manufacturing ramping up throughout 2028. During this period, the industry will focus on perfecting the chemistry of "resists" and the durability of "pellicles"—protective covers for the photomasks—which must withstand the intense power of the High-NA EUV light source without degrading.

Near-term developments will likely include the announcement of "Hyper-NA" lithography research. ASML is already exploring systems with numerical apertures exceeding 0.75, which would be required for nodes beyond 1nm (the 10A node and beyond). Experts predict that the lessons learned from Intel’s current High-NA rollout in Portland will directly inform the design of these future machines. Challenges remain, particularly in the realm of power consumption; these scanners require massive amounts of electricity, and fab operators will need to integrate sustainable energy solutions to manage the carbon footprint of 1.4nm production.

A New Era for Silicon

The completion of Intel’s second High-NA EUV installation marks a definitive "coming of age" for 1.4nm technology. By hitting the 175 WPH throughput target with the EXE:5200B, Intel has provided the first concrete evidence that the industry can move beyond the limitations of standard EUV. This development is a significant victory for Intel’s turnaround strategy and a clear signal to the market that the company intends to lead the AI hardware revolution from the foundational level of the transistor.

As we move into the middle of 2026, the focus will shift from installation to execution. The industry will be watching for Intel’s first 14A test chips and the eventual announcement of major foundry customers. While the path to 1.4nm is fraught with technical and financial hurdles, the successful operationalization of High-NA EUV in Portland suggests that the "geometric scaling" era is far from over. For the tech industry, the message is clear: the next decade of AI innovation will be printed with High-NA light.

This content is intended for informational purposes only and represents analysis of current AI developments.

TokenRing AI delivers enterprise-grade solutions for multi-agent AI workflow orchestration, AI-powered development tools, and seamless remote collaboration platforms.

For more information, visit https://www.tokenring.ai/.