As of January 19, 2026, the global semiconductor landscape has undergone a tectonic shift. After nearly a decade of playing catch-up to Asian rivals, Intel (NASDAQ: INTC) has officially entered high-volume manufacturing (HVM) for its 18A (1.8nm-class) process node. This milestone marks the successful completion of CEO Pat Gelsinger’s audacious "five nodes in four years" roadmap, a feat many industry skeptics deemed impossible when it was first announced. The 18A node is not merely a technical incremental step; it is the cornerstone of Intel’s "IDM 2.0" strategy, designed to transform the company into a world-class foundry that rivals TSMC (NYSE: TSM) while simultaneously powering its own next-generation AI silicon.

The immediate significance of 18A lies in its marriage of two revolutionary technologies: RibbonFET and PowerVia. By being the first to bring backside power delivery and gate-all-around (GAA) transistors to the mass market at this scale, Intel has effectively leapfrogged its competitors in performance-per-watt efficiency. With the first "Panther Lake" consumer chips hitting shelves next week and "Clearwater Forest" Xeon processors already shipping to hyperscale data centers, 18A has moved from a laboratory ambition to the primary engine of the AI hardware revolution.

The Architecture of Dominance: RibbonFET and PowerVia

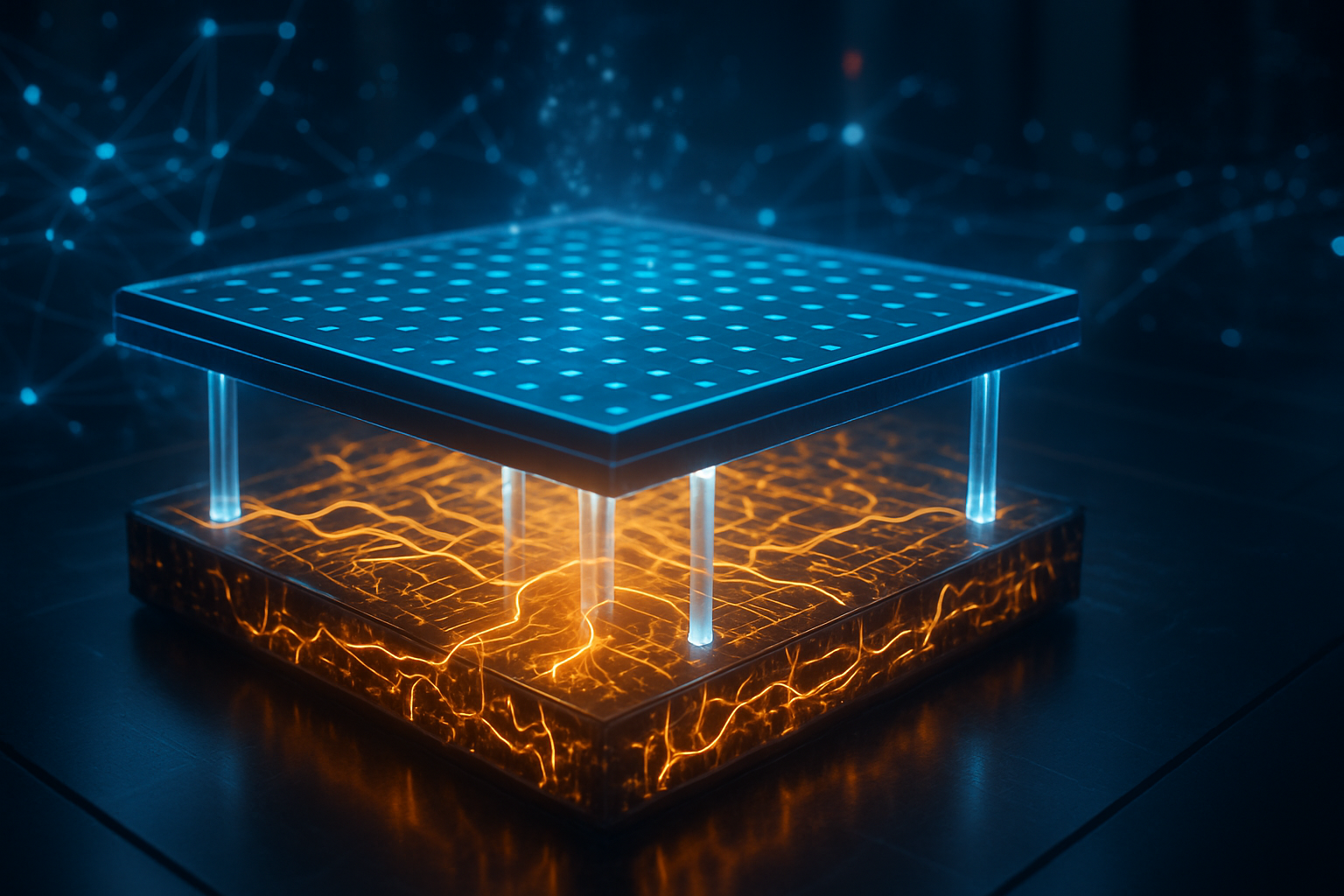

Technically, 18A represents the most significant architectural overhaul in semiconductor manufacturing since the introduction of FinFET over a decade ago. At the heart of the node is RibbonFET, Intel's implementation of Gate-All-Around (GAA) transistor technology. Unlike the previous FinFET design, where the gate contacted the channel on three sides, RibbonFET stacks multiple nanoribbons vertically, with the gate wrapping entirely around the channel. This configuration provides superior electrostatic control, drastically reducing current leakage and allowing transistors to switch faster at significantly lower voltages. Industry experts note that this level of control is essential for the high-frequency demands of modern AI training and inference.

Complementing RibbonFET is PowerVia, Intel’s proprietary version of backside power delivery. Historically, both power and data signals competed for space on the front of the silicon wafer, leading to a "congested" wiring environment that caused electrical interference and voltage droop. PowerVia moves the entire power delivery network to the back of the wafer, decoupling it from the signal routing on the top. This innovation allows for up to a 30% increase in transistor density and a significant boost in power efficiency. While TSMC (NYSE: TSM) has opted to wait until its A16 node to implement similar backside power tech, Intel’s "first-mover" advantage with PowerVia has given it a roughly 18-month lead in this specific power-delivery architecture.

Initial reactions from the semiconductor research community have been overwhelmingly positive. TechInsights and other industry analysts have reported that 18A yields have crossed the 65% threshold—a critical "gold standard" for commercial viability. Experts suggest that by separating power and signal, Intel has solved one of the most persistent bottlenecks in chip design: the "RC delay" that occurs when signals travel through thin, high-resistance wires. This technical breakthrough has allowed Intel to reclaim the title of the world’s most advanced logic manufacturer, at least for the current 2026 cycle.

A New Customer Portfolio: Microsoft, Amazon, and the Apple Pivot

The success of 18A has fundamentally altered the competitive dynamics of the foundry market. Intel Foundry has successfully secured several "whale" customers who were previously exclusive to TSMC. Most notably, Microsoft (NASDAQ: MSFT) has confirmed that its next generation of custom Maia AI accelerators is being manufactured on the 18A node. Similarly, Amazon (NASDAQ: AMZN) has partnered with Intel to produce custom AI fabric silicon for its AWS Graviton and Trainium 3 platforms. These wins demonstrate that the world’s largest cloud providers are no longer willing to rely on a single source for their most critical AI infrastructure.

Perhaps the most shocking development of late 2025 was the revelation that Apple (NASDAQ: AAPL) had qualified Intel 18A for a portion of its M-series silicon production. While TSMC remains Apple’s primary partner, the move to Intel for entry-level MacBook and iPad chips marks the first time in a decade that Apple has diversified its cutting-edge logic manufacturing. For Intel, this is a massive validation of the IDM 2.0 model, proving that its foundry services can meet the exacting standards of the world’s most demanding hardware company.

This shift puts immense pressure on NVIDIA (NASDAQ: NVDA) and Advanced Micro Devices (NASDAQ: AMD). While NVIDIA has traditionally been conservative with its foundry choices, the superior performance-per-watt of 18A—specifically for high-density AI clusters—has led to persistent rumors that NVIDIA’s "Rubin" successor might utilize a multi-foundry approach involving Intel. The strategic advantage for these companies lies in supply chain resilience; by utilizing Intel’s domestic Fabs in Arizona and Ohio, they can mitigate the geopolitical risks associated with manufacturing exclusively in the Taiwan Strait.

Geopolitics and the AI Power Struggle

The broader significance of Intel’s 18A achievement cannot be overstated. It represents a pivot point for Western semiconductor sovereignty. As AI becomes the defining technology of the decade, the ability to manufacture the underlying chips domestically is now a matter of national security. Intel’s progress is a clear win for the U.S. CHIPS Act, as much of the 18A capacity is housed in the newly operational Fab 52 in Arizona. This domestic "leading-edge" capability provides a cushion against global supply chain shocks that have plagued the industry in years past.

In the context of the AI landscape, 18A arrives at a time when the "power wall" has become the primary limit on AI model growth. As LLMs (Large Language Models) grow in complexity, the energy required to train and run them has skyrocketed. The efficiency gains provided by PowerVia and RibbonFET are precisely what hyperscalers like Meta (NASDAQ: META) and Alphabet (NASDAQ: GOOGL) need to keep their AI ambitions sustainable. By reducing the energy footprint of each transistor switch, Intel 18A is effectively enabling the next order of magnitude in AI compute scaling.

However, challenges remain. While Intel leads in backside power, TSMC’s N2 node still maintains a slight advantage in absolute SRAM density—the memory used for on-chip caches that are vital for AI performance. The industry is watching closely to see if Intel can maintain its execution momentum as it transitions from 18A to the even more ambitious 14A node. The comparison to the "14nm era," where Intel remained stuck on a single node for years, is frequently cited by skeptics as a cautionary tale.

The Road to 14A and High-NA EUV

Looking ahead, the 18A node is just the beginning of Intel’s long-term roadmap. The company has already begun "risk production" for its 14A node, which will be the first in the world to utilize High-NA (Numerical Aperture) EUV lithography from ASML (NASDAQ: ASML). This next-generation machinery allows for even finer features to be printed on silicon, potentially pushing transistor counts into the hundreds of billions on a single die. Experts predict that 14A will be the node that truly determines if Intel can hold its lead through the end of the decade.

In the near term, we can expect a flurry of 18A-based product announcements throughout 2026. Beyond CPUs and AI accelerators, the 18A node is expected to be a popular choice for automotive silicon and high-performance networking chips, where the combination of high speed and low heat is critical. The primary challenge for Intel now is "scaling the ecosystem"—ensuring that the design tools (EDA) and IP blocks from partners like Synopsys (NASDAQ: SNPS) and Cadence (NASDAQ: CDNS) are fully optimized for the unique power-delivery characteristics of 18A.

Final Verdict: A New Chapter for Silicon Valley

The successful rollout of Intel 18A is a watershed moment in the history of computing. It signifies the end of Intel’s "stagnation" era and the birth of a viable, Western-led alternative to the TSMC monopoly. For the AI industry, 18A provides the necessary hardware foundation to continue the current pace of innovation, offering a path to higher performance without a proportional increase in energy consumption.

In the coming weeks and months, the focus will shift from "can they build it?" to "how much can they build?" Yield consistency and the speed of the Arizona Fab ramp-up will be the key metrics for investors and customers alike. While TSMC is already preparing its A16 response, for the first time in many years, Intel is not the one playing catch-up—it is the one setting the pace.

This content is intended for informational purposes only and represents analysis of current AI developments.

TokenRing AI delivers enterprise-grade solutions for multi-agent AI workflow orchestration, AI-powered development tools, and seamless remote collaboration platforms.

For more information, visit https://www.tokenring.ai/.