As of January 20, 2026, the artificial intelligence industry has reached a pivotal juncture where software sophistication is once again being outpaced by the physical limitations of hardware. Following major announcements at CES 2026, it has become clear that the traditional organic substrates used to house the world’s most powerful chips have reached their breaking point. The industry is now racing toward a "Glass Age," as glass substrates emerge as the critical bottleneck determining which companies will dominate the next era of generative AI and sovereign supercomputing.

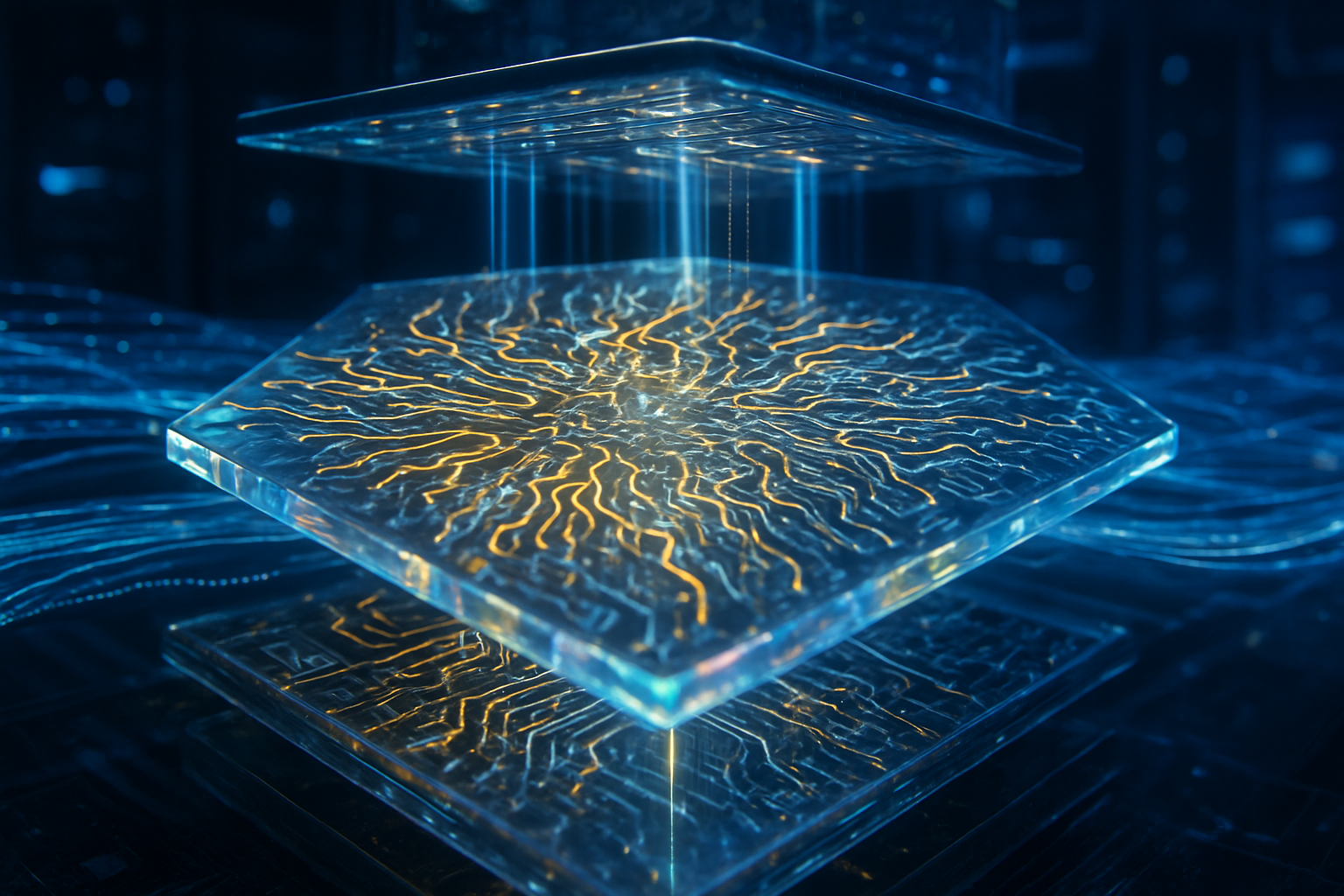

The shift is not merely an incremental upgrade but a fundamental re-engineering of how chips are packaged. For decades, the industry relied on organic materials like Ajinomoto Build-up Film (ABF) to connect silicon to circuit boards. However, the massive thermal loads—often exceeding 1,000 watts—generated by modern AI accelerators have caused these organic materials to warp and fail. Glass, with its superior thermal stability and rigidity, has transitioned from a laboratory curiosity to the must-have architecture for the next generation of high-performance computing.

The Technical Leap: Solving the Scaling Crisis

The technical shift toward glass-core substrates is driven by three primary factors: thermal expansion, interconnect density, and structural integrity. Organic substrates possess a Coefficient of Thermal Expansion (CTE) that differs significantly from silicon, leading to mechanical stress and "warpage" as chips heat and cool. In contrast, glass can be engineered to match the CTE of silicon almost perfectly. This stability allows for the creation of massive, "reticle-busting" packages exceeding 100mm x 100mm, which are necessary to house the sprawling arrays of chiplets and HBM4 memory stacks that define 2026-era AI hardware.

Furthermore, glass enables a 10x increase in through-glass via (TGV) density compared to the vias possible in organic layers. This allows for much finer routing—down to sub-2-micron line spacing—enabling faster data transfer between chiplets. Intel (NASDAQ: INTC) has taken an early lead in this space, announcing this month that its Xeon 6+ "Clearwater Forest" processor has officially entered High-Volume Manufacturing (HVM). This marks the first time a commercial CPU has utilized a glass-core substrate, proving that the technology is ready for the rigors of the modern data center.

The reaction from the research community has been one of cautious optimism tempered by the reality of manufacturing yields. While glass offers unparalleled electrical performance and supports signaling speeds of up to 448 Gbps, its brittle nature makes it difficult to handle in the massive 600mm x 600mm panel formats used in modern factories. Initial yields are reported to be in the 75-85% range, significantly lower than the 95%+ yields common with organic substrates, creating an immediate supply-side bottleneck for the industry's largest players.

Strategic Realignments: Winners and Losers

The transition to glass is reshuffling the competitive hierarchy of the semiconductor world. Intel’s decade-long investment in glass research has granted it a significant first-mover advantage, potentially allowing it to regain market share in the high-end server market. Meanwhile, Samsung (KRX: 005930) has leveraged its expertise in display technology to form a "Triple Alliance" between its semiconductor, display, and electro-mechanics divisions. This vertical integration aims to provide a turnkey glass-substrate solution for custom AI ASICs by late 2026, positioning Samsung as a formidable rival to the traditional foundry models.

TSMC (NYSE: TSM), the current king of AI chip manufacturing, finds itself in a more complex position. While it continues to dominate the market with its silicon-based CoWoS (Chip-on-Wafer-on-Substrate) technology for NVIDIA (NASDAQ: NVDA), TSMC's full-scale glass-based CoPoS (Chip-on-Panel-on-Substrate) platform is not expected to reach mass production until 2027 or 2028. This delay has created a strategic window for competitors and has forced companies like AMD (NASDAQ: AMD) to explore partnerships with SK Hynix (KRX: 000660) and its subsidiary, Absolics, which recently began shipping glass substrate samples from its new $600 million facility in Georgia.

For AI startups and labs, this bottleneck means that the cost of compute is likely to remain high. As the industry moves away from commodity organic substrates toward specialized glass, the supply chain is tightening. The strategic advantage now lies with those who can secure guaranteed capacity from the few facilities capable of handling glass, such as those owned by Intel or the emerging SK Hynix-Absolics ecosystem. Companies that fail to pivot their chip architectures toward glass may find themselves literally unable to cool their next-generation designs.

The Warpage Wall and Wider Significance

The "Warpage Wall" is the hardware equivalent of the "Scaling Law" debate in AI software. Just as researchers question how much further LLMs can scale with existing data, hardware engineers have realized that AI performance cannot scale further with existing materials. The broader significance of glass substrates lies in their ability to act as a platform for Co-Packaged Optics (CPO). Because glass is transparent, it allows for the integration of optical interconnects directly into the chip package, replacing copper wires with light-speed data transmission—a necessity for the trillion-parameter models currently under development.

However, this transition has exposed a dangerous single-source dependency in the global supply chain. The industry is currently reliant on a handful of specialized materials firms, most notably Nitto Boseki (TYO: 3110), which provides the high-end glass cloth required for these substrates. A projected 10-20% supply gap for high-grade glass materials in 2026 has sent shockwaves through the industry, drawing comparisons to the substrate shortages of 2021. This scarcity is turning glass from a technical choice into a geopolitical and economic lever.

The move to glass also marks the final departure from the "Moore's Law" era of simple transistor scaling. We have entered the era of "System-on-Package," where the substrate is just as important as the silicon itself. Similar to the introduction of High Bandwidth Memory (HBM) or EUV lithography, the adoption of glass substrates represents a "no-turning-back" milestone. It is the foundation upon which the next decade of AI progress will be built, but it comes with the risk of further concentrating power in the hands of the few companies that can master its complex manufacturing.

Future Horizons: Beyond the Pilot Phase

Looking ahead, the next 24 months will be defined by the "yield race." While Intel is currently the only firm in high-volume manufacturing, Samsung and Absolics are expected to ramp up their production lines by the end of 2026. Experts predict that once yields stabilize above 90%, the industry will see a flood of new chip designs that take advantage of the 100mm+ package sizes glass allows. This will likely lead to a new class of "Super-GPUs" that combine dozens of chiplets into a single, massive compute unit.

One of the most anticipated applications on the horizon is the integration of glass substrates into edge AI devices. While the current focus is on massive data center chips, the superior electrical properties of glass could eventually allow for thinner, more powerful AI-integrated laptops and smartphones. However, the immediate challenge remains the high cost of the specialized manufacturing equipment provided by firms like Applied Materials (NASDAQ: AMAT), which currently face a multi-year backlog for glass-processing tools.

The Verdict on the Glass Transition

The transition to glass substrates is more than a technical footnote; it is the physical manifestation of the AI industry's insatiable demand for power and speed. As organic materials fail under the heat of the AI revolution, glass provides the necessary structural and thermal foundation for the future. The current bottleneck is a symptom of a massive industrial pivot—one that favors first-movers like Intel and materials giants like Corning (NYSE: GLW) and Nitto Boseki.

In summary, the next few months will be critical as more manufacturers transition from pilot samples to high-volume production. The industry must navigate a fragile supply chain and solve significant yield challenges to avoid a prolonged hardware shortage. For now, the "Glass Age" has officially begun, and it will be the defining factor in which AI architectures can survive the intense heat of the coming years. Keep a close eye on yield reports from the new Georgia and Arizona facilities; they will be the best indicators of whether the AI hardware train can keep its current momentum.

This content is intended for informational purposes only and represents analysis of current AI developments.

TokenRing AI delivers enterprise-grade solutions for multi-agent AI workflow orchestration, AI-powered development tools, and seamless remote collaboration platforms.

For more information, visit https://www.tokenring.ai/.